數(shù)字集成電路設(shè)計 架構(gòu)創(chuàng)新與系統(tǒng)集成的未來之路

隨著全球數(shù)字化轉(zhuǎn)型浪潮的推進,數(shù)字集成電路作為信息產(chǎn)業(yè)的基石,其設(shè)計理念與技術(shù)路徑正經(jīng)歷著深刻變革。在創(chuàng)言與合創(chuàng)資本劉華瑞的探討中,數(shù)字集成電路設(shè)計的關(guān)注點已從單一的性能提升,轉(zhuǎn)向更復(fù)雜的系統(tǒng)級優(yōu)化與生態(tài)構(gòu)建。

一、架構(gòu)創(chuàng)新:從專用到可重構(gòu)

傳統(tǒng)數(shù)字集成電路設(shè)計往往圍繞特定功能展開,追求在固定架構(gòu)下的性能極致。面對多樣化的應(yīng)用場景,如人工智能、自動駕駛、物聯(lián)網(wǎng)等,專用架構(gòu)的局限性日益凸顯。劉華瑞指出,未來的關(guān)注點將聚焦于可重構(gòu)計算架構(gòu),如FPGA與異構(gòu)計算平臺,它們能夠通過軟件定義硬件,靈活適應(yīng)不同算法與工作負載,實現(xiàn)效率與通用性的平衡。這種架構(gòu)創(chuàng)新不僅提升了芯片的適應(yīng)性,也降低了研發(fā)周期與成本,為新興應(yīng)用快速落地提供了可能。

二、系統(tǒng)集成:從芯片到“芯片級系統(tǒng)”

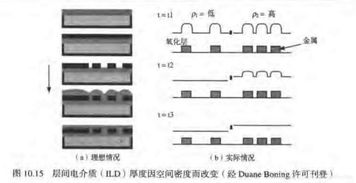

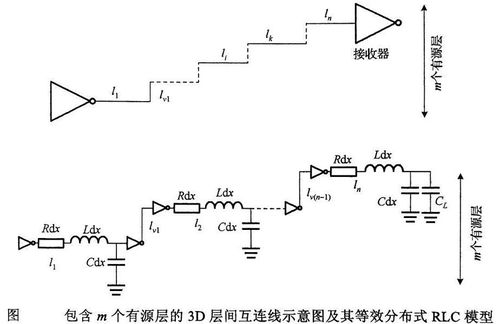

隨著工藝節(jié)點逼近物理極限,單純依靠制程微縮帶來的性能增益已逐漸放緩。數(shù)字集成電路設(shè)計的重心正轉(zhuǎn)向系統(tǒng)級集成,即通過先進封裝技術(shù)(如Chiplet、3D堆疊)將多個功能模塊整合為“芯片級系統(tǒng)”。劉華瑞強調(diào),這種設(shè)計范式能夠突破單芯片的面積與功耗限制,實現(xiàn)內(nèi)存、計算、通信等單元的高效協(xié)同,從而提升整體性能與能效。它促進了產(chǎn)業(yè)鏈的分工協(xié)作,允許設(shè)計者復(fù)用成熟模塊,加速產(chǎn)品迭代。

三、設(shè)計方法學(xué):自動化與智能化并行

數(shù)字集成電路的復(fù)雜度呈指數(shù)級增長,傳統(tǒng)設(shè)計方法已難以應(yīng)對。因此,設(shè)計方法學(xué)的革新成為關(guān)鍵關(guān)注點。一方面,EDA工具正朝著更高度的自動化發(fā)展,通過高層次綜合(HLS)等技術(shù),將算法描述直接轉(zhuǎn)換為硬件電路,降低設(shè)計門檻;另一方面,人工智能開始滲透到設(shè)計流程中,用于優(yōu)化布局布線、功耗預(yù)測等環(huán)節(jié),提升設(shè)計效率與可靠性。劉華瑞認為,人機協(xié)同的設(shè)計模式將成為主流,推動數(shù)字集成電路向更智能、更自主的方向演進。

四、生態(tài)構(gòu)建:開放協(xié)作與安全可信

數(shù)字集成電路的設(shè)計不再局限于技術(shù)本身,生態(tài)系統(tǒng)的構(gòu)建同樣至關(guān)重要。開源指令集架構(gòu)(如RISC-V)的興起,打破了傳統(tǒng)封閉生態(tài)的壟斷,為創(chuàng)新者提供了更靈活的選擇。劉華瑞提到,合創(chuàng)資本關(guān)注那些基于開放生態(tài)、聚焦垂直領(lǐng)域的設(shè)計企業(yè),它們能夠通過協(xié)作加速技術(shù)落地。隨著芯片在關(guān)鍵基礎(chǔ)設(shè)施中的廣泛應(yīng)用,安全與可信設(shè)計成為不可或缺的一環(huán),從硬件層面保障數(shù)據(jù)隱私與系統(tǒng)韌性。

###

數(shù)字集成電路設(shè)計正站在新的十字路口,架構(gòu)創(chuàng)新、系統(tǒng)集成、方法學(xué)革新與生態(tài)構(gòu)建共同勾勒出未來圖景。劉華瑞表示,投資者與設(shè)計者需擁抱這些變化,在技術(shù)深度與市場廣度間尋找平衡,以推動集成電路產(chǎn)業(yè)持續(xù)突破邊界,賦能千行百業(yè)的智能化轉(zhuǎn)型。

如若轉(zhuǎn)載,請注明出處:http://www.51major.com.cn/product/59.html

更新時間:2026-01-07 11:54:53