基于NMOS與升降壓驅(qū)動(dòng)IC的防反接保護(hù)電路設(shè)計(jì)

在現(xiàn)代電子系統(tǒng)中,電源反接是導(dǎo)致電路損壞的常見原因之一。傳統(tǒng)的二極管防反接方案雖然簡(jiǎn)單,但存在正向壓降大、效率低的問題。本文將介紹一種結(jié)合NMOS晶體管和升降壓驅(qū)動(dòng)IC的高效防反接保護(hù)電路設(shè)計(jì)方案,適用于集成電路設(shè)計(jì)領(lǐng)域。

一、防反接保護(hù)電路的基本原理

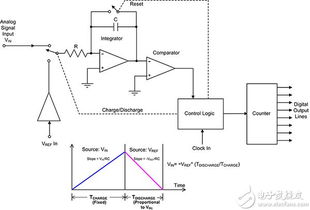

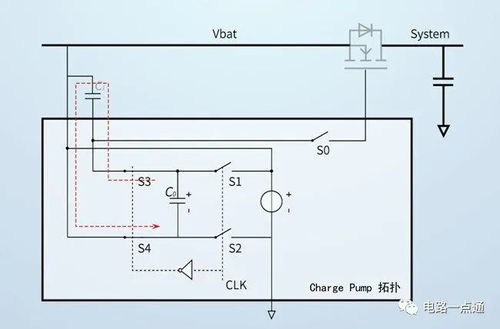

防反接保護(hù)的核心目標(biāo)是在電源極性接反時(shí)自動(dòng)切斷供電通路。NMOS晶體管因其低導(dǎo)通電阻(Rds(on))特性成為理想選擇。當(dāng)電源正確連接時(shí),NMOS導(dǎo)通;反接時(shí),NMOS截止,從而實(shí)現(xiàn)保護(hù)。

二、NMOS防反接電路的工作機(jī)制

- 正接保護(hù):電源正極通過負(fù)載連接到NMOS的漏極(D),源極(S)接地。通過升降壓驅(qū)動(dòng)IC產(chǎn)生一個(gè)高于輸入電壓的柵極驅(qū)動(dòng)電壓,使NMOS完全導(dǎo)通。

- 反接保護(hù):當(dāng)電源反接時(shí),NMOS的體二極管處于反向偏置狀態(tài),電路無(wú)法形成通路,有效保護(hù)后端電路。

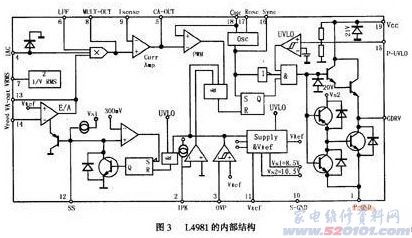

三、升降壓驅(qū)動(dòng)IC的關(guān)鍵作用

升降壓驅(qū)動(dòng)IC在此設(shè)計(jì)中承擔(dān)兩個(gè)重要功能:

- 柵極電壓生成:產(chǎn)生高于輸入電壓的驅(qū)動(dòng)信號(hào),確保NMOS在低輸入電壓下也能完全導(dǎo)通

- 動(dòng)態(tài)控制:根據(jù)輸入電壓變化實(shí)時(shí)調(diào)整柵極驅(qū)動(dòng)電平,優(yōu)化效率表現(xiàn)

四、具體電路設(shè)計(jì)實(shí)現(xiàn)

- NMOS選型要點(diǎn):

- 低導(dǎo)通電阻(通常<10mΩ)

- 合適的電壓額定值

- 優(yōu)化的封裝形式以降低熱阻

- 升降壓驅(qū)動(dòng)IC配置:

- 采用電荷泵或boost架構(gòu)

- 集成過壓、欠壓保護(hù)功能

- 支持寬輸入電壓范圍(如2.7V至36V)

- 外圍元件設(shè)計(jì):

- 柵極驅(qū)動(dòng)電阻優(yōu)化

- 濾波電容配置

- ESD保護(hù)電路

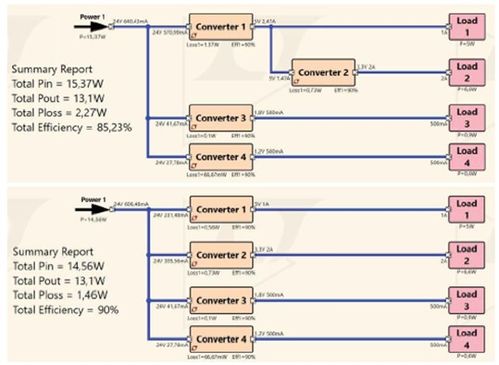

五、性能優(yōu)勢(shì)分析

- 高效率:相比二極管方案,功率損耗降低90%以上

- 低電壓降:導(dǎo)通壓降可低至毫伏級(jí)別

- 快速響應(yīng):反接保護(hù)響應(yīng)時(shí)間<1μs

- 熱性能優(yōu)異:顯著降低系統(tǒng)溫升

六、集成電路設(shè)計(jì)考量

在IC設(shè)計(jì)層面需要特別注意:

- 布局優(yōu)化:功率路徑最短化設(shè)計(jì)

- 熱管理:集成溫度監(jiān)測(cè)和保護(hù)

- EMC設(shè)計(jì):降低開關(guān)噪聲干擾

- 工藝選擇:根據(jù)電壓等級(jí)選擇合適的BCD工藝

七、應(yīng)用場(chǎng)景

本方案特別適用于:

- 汽車電子系統(tǒng)

- 工業(yè)控制設(shè)備

- 便攜式電子產(chǎn)品

- 電池供電系統(tǒng)

八、設(shè)計(jì)驗(yàn)證要點(diǎn)

- 反接耐受測(cè)試:驗(yàn)證保護(hù)電路的可靠性

- 效率測(cè)試:在不同負(fù)載條件下評(píng)估性能

- 熱測(cè)試:確保在極限工況下的穩(wěn)定性

- EMC測(cè)試:滿足相關(guān)電磁兼容標(biāo)準(zhǔn)

基于NMOS和升降壓驅(qū)動(dòng)IC的防反接保護(hù)電路設(shè)計(jì),通過創(chuàng)新的架構(gòu)實(shí)現(xiàn)了高效率、低損耗的保護(hù)功能。這種方案不僅提升了系統(tǒng)可靠性,還顯著改善了整體能效表現(xiàn),為現(xiàn)代電子設(shè)備提供了一種優(yōu)質(zhì)的電源保護(hù)解決方案。隨著集成電路技術(shù)的不斷發(fā)展,這種設(shè)計(jì)方案將在更多領(lǐng)域展現(xiàn)其價(jià)值。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.51major.com.cn/product/33.html

更新時(shí)間:2026-01-07 05:03:44