錄音芯片集成電路設(shè)計 技術(shù)原理、設(shè)計挑戰(zhàn)與應(yīng)用前景

錄音芯片作為現(xiàn)代電子設(shè)備中不可或缺的組成部分,廣泛應(yīng)用于消費電子、安防監(jiān)控、語音識別及物聯(lián)網(wǎng)等領(lǐng)域。其集成電路設(shè)計不僅涉及模擬和數(shù)字電路的深度融合,還要求設(shè)計者在功耗、性能、成本和集成度之間取得平衡。本文將探討錄音芯片集成電路設(shè)計的技術(shù)原理、設(shè)計挑戰(zhàn)以及未來發(fā)展趨勢。

一、錄音芯片的基本原理與結(jié)構(gòu)

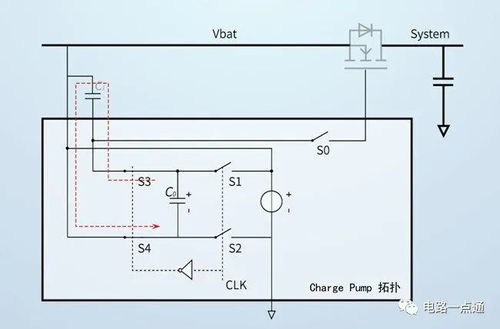

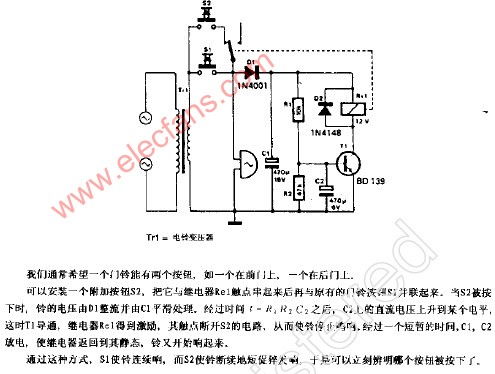

錄音芯片的核心功能是實現(xiàn)聲音信號的采集、處理和存儲。其典型結(jié)構(gòu)包括麥克風(fēng)前置放大器、模數(shù)轉(zhuǎn)換器(ADC)、數(shù)字信號處理器(DSP)以及存儲接口。麥克風(fēng)前置放大器負責(zé)放大來自麥克風(fēng)的微弱模擬信號,模數(shù)轉(zhuǎn)換器將模擬信號轉(zhuǎn)換為數(shù)字信號,而數(shù)字信號處理器則對數(shù)字信號進行濾波、壓縮和編碼。處理后的數(shù)據(jù)通過存儲接口保存到外部存儲器或內(nèi)部緩存中。現(xiàn)代錄音芯片還集成了低功耗管理單元和通信接口(如I2C、SPI),以支持智能喚醒和外部控制。

二、設(shè)計中的關(guān)鍵挑戰(zhàn)

錄音芯片集成電路設(shè)計面臨多重挑戰(zhàn)。噪聲控制是核心難題。由于聲音信號本身微弱,設(shè)計時需采用低噪聲放大器和高精度ADC,同時通過屏蔽和布局優(yōu)化減少電磁干擾。功耗管理尤為重要,尤其在便攜式設(shè)備中。設(shè)計者需采用動態(tài)電壓頻率調(diào)整(DVFS)和休眠模式技術(shù),以延長電池壽命。集成度與成本之間的權(quán)衡也不容忽視。高集成度雖能縮小芯片面積,但可能增加工藝復(fù)雜性和測試成本。兼容性與標(biāo)準(zhǔn)化問題需在設(shè)計初期考慮,例如支持多種音頻格式(如PCM、MP3)和接口協(xié)議。

三、設(shè)計流程與方法

錄音芯片的設(shè)計流程通常包括需求分析、架構(gòu)設(shè)計、電路仿真、版圖設(shè)計和測試驗證。在需求分析階段,設(shè)計團隊需明確應(yīng)用場景的性能指標(biāo),如信噪比(SNR)、動態(tài)范圍和功耗預(yù)算。架構(gòu)設(shè)計階段決定功能模塊的劃分和交互方式,例如選擇基于ARM核的SoC方案或?qū)S肈SP核。電路仿真使用EDA工具(如Cadence、Synopsys)對模擬和數(shù)字部分進行驗證,確保信號完整性和時序正確性。版圖設(shè)計則涉及物理布局,需遵循深亞微米工藝規(guī)則,以避免寄生效應(yīng)和熱問題。通過流片和測試,驗證芯片的實際性能。

四、應(yīng)用領(lǐng)域與發(fā)展趨勢

錄音芯片已廣泛應(yīng)用于智能手機、智能家居、汽車電子和醫(yī)療設(shè)備中。例如,在語音助手中,它實現(xiàn)高精度語音采集;在安防監(jiān)控中,支持長時間錄音與事件觸發(fā)存儲。未來,隨著人工智能和5G技術(shù)的普及,錄音芯片正朝著智能化、低功耗和高集成方向演進。邊緣計算能力的集成將使其具備本地語音識別和噪聲抑制功能,而新材料(如MEMS麥克風(fēng))和先進工藝(如FinFET)的應(yīng)用將進一步提升性能。綠色設(shè)計理念將推動低功耗和可回收材料的使用,以滿足可持續(xù)發(fā)展需求。

結(jié)語

錄音芯片集成電路設(shè)計是一個多學(xué)科交叉的領(lǐng)域,融合了電子工程、計算機科學(xué)和材料技術(shù)。面對日益增長的市場需求,設(shè)計者需不斷創(chuàng)新,優(yōu)化架構(gòu)與工藝,以推出更高效、可靠的解決方案。隨著技術(shù)演進,錄音芯片將繼續(xù)賦能智能設(shè)備,推動人機交互的革新。

如若轉(zhuǎn)載,請注明出處:http://www.51major.com.cn/product/15.html

更新時間:2026-01-09 05:36:31